# **MAX32660 USER GUIDE**

UG6659; Rev 1; 07/2021

**Abstract:** This user guide provides application developers information on how to use the memory and peripherals of the MAX32660 microcontroller. Detailed information for all registers and fields in the device are covered. Guidance is given for managing the clocks, power and initialization of the product.

# **Table of Contents**

| 1.  | Introd | uction                                                     | 14 |

|-----|--------|------------------------------------------------------------|----|

| 1   | 1 Rel  | ated Documentation                                         | 14 |

| 1   | 2 Cor  | nventions Used in this Document                            | 14 |

|     | 1.2.1  | Number Notations                                           | 14 |

|     | 1.2.2  | Register and Field Access Definitions                      |    |

|     | 1.2.3  | Register Lists                                             |    |

|     | 1.2.4  | Register Detail Tables                                     |    |

| 2.  | Overvi | iew                                                        |    |

| 3.  | Memo   | ory, Register Mapping, and Access                          | 17 |

| 3   | 1 Ove  | erview                                                     | 17 |

| 3   | 2 Sta  | ndard Memory Regions                                       | 19 |

|     | 3.2.1  | Code Space                                                 | 20 |

|     | 3.2.2  | SRAM Space                                                 | 20 |

|     | 3.2.3  | Peripheral Space                                           | 20 |

|     | 3.2.4  | System Area (Private Peripheral Bus)                       | 21 |

| 3   | 3 Dei  | vice Memory Instances                                      | 21 |

|     | 3.3.1  | Main Program Flash Memory                                  | 21 |

|     | 3.3.2  | Instruction Cache Memory                                   | 21 |

|     | 3.3.3  | Information Block Flash Memory                             | 21 |

|     | 3.3.4  | System SRAM                                                | 22 |

| 3.4 | 4 AH   | B Bus Matrix and AHB Bus Interfaces                        | 22 |

|     | 3.4.1  | Core AHB Interface                                         | 22 |

|     | 3.4.2  | AHB Slaves                                                 | 22 |

| 3.  | 5 Per  | ripheral Register Map                                      | 22 |

|     | 3.5.1  | APB Peripheral Base Address Map                            | 22 |

| 4.  | Systen | n, Power, Clocks, Reset                                    | 24 |

| 4.  | 1 Cor  | re Operating Voltage Range Selection                       | 24 |

|     | 4.1.1  | Setting the Operating Voltage Range                        | 24 |

|     | 4.1.2  | Flash Wait States                                          | 25 |

| 4.  | 2 Osc  | cillator Sources and Clock Switching                       | 27 |

|     | 4.2.1  | Oscillator Implementation                                  | 28 |

|     | 4.2.2  | High-Frequency Internal Oscillator (HFIO)                  | 29 |

|     | 4.2.3  | 32.768kHz External Crystal or Clock (X32K)                 | 29 |

|     | 4.2.4  | 80kHz Ultra-Low Power Nano-Ring Internal Oscillator (NANO) | 30 |

| 4.  | 3 Ор   | erating Modes                                              | 30 |

|     | 4.3.1  | ACTIVE                                                     | 30 |

|     | 4.3.2  | Low-Power Modes                                            | 30 |

| 4.4 | 4 Shu  | ıtdown                                                     | 32 |

| 4.  | 5 De   | vice Resets                                                | 32 |

|     | 4.5.1  | Peripheral Reset                                           | 34 |

|     | 4.5.2  | Soft Reset                                                 | 34 |

|     | 4.5.3  | System Reset                                               | 34 |

|     | 4.5.4  | Power-On Reset                                             | 34 |

|    | 4.6  | Instruction Cache Controller (ICC)                      | 35  |

|----|------|---------------------------------------------------------|-----|

|    | 4.6  | 6.1 Enabling the ICC                                    | 35  |

|    | 4.6  | 6.2 Disabling the ICC                                   | 35  |

|    |      | 6.3 Flushing the ICC's Cache and Tag RAM                |     |

|    |      | 6.4 Invalidating the ICC's Cache                        |     |

|    |      | 6.5 Zeroizing the ICC's Cache and Tag RAM               |     |

|    | 4.7  | ICC Registers                                           | 35  |

|    | 4.7  | 7.1 ICC Register Details                                |     |

|    | 4.8  | RAM Memory Management                                   | 37  |

|    | 4.8  | 8.1 System RAM                                          | 37  |

|    | 4.8  | 8.2 RAM Zeroization                                     |     |

|    | 4.8  | 8.3 RAM Low-Power Modes                                 | 37  |

|    | 4.9  | Global Control Registers (GCR)                          | 37  |

|    | 4.9  | 9.1 Global Control Register Details                     | 38  |

|    | 4.10 | System Initialization Registers (SIR)                   |     |

|    | 1.   | 10.1 System Initialization Register Details             | 16  |

|    | 4.11 | Power Sequencer and Always-On-Domain Registers (PWRSEQ) |     |

|    |      |                                                         |     |

| _  |      | 11.1 Power Sequencer Register Details                   |     |

| 5. | Int  | terrupts and Exceptions                                 | 52  |

|    | 5.1  | Features                                                | 52  |

|    | 5.2  | Interrupt Vector Table                                  | 52  |

|    |      | ·                                                       |     |

| 6. | De   | ebug Access Port (DAP)                                  | 54  |

|    | 6.1  | Instances                                               | 54  |

|    | 6.2  | Access Control                                          | 54  |

|    | 6 '  | 2.1 Factory-Disabled DAP                                | 5.4 |

|    | _    | 2.2 Software-Accessible DAP                             |     |

|    | 6.3  | Pin Configuration                                       |     |

|    |      |                                                         |     |

| 7. | Fla  | ash Controller (FLC)                                    | 55  |

|    | 7.1  | Instances                                               | 55  |

|    | 7.2  | Usage                                                   | 55  |

|    |      | 2.1 Clock Configuration                                 |     |

|    |      | 2.2 Lock Protection                                     |     |

|    |      | 2.3 Flash Write Width                                   |     |

|    |      | 2.4 Flash Write                                         |     |

|    |      | 2.5 Page Erase                                          |     |

|    |      | 2.6 Mass Erase                                          |     |

|    | 7.3  | Flash Controller Registers                              |     |

|    | 7:   | 3.1 Register Details                                    | 59  |

| 8. |      | eneral-Purpose I/O and Alternate Function Pins          |     |

|    |      | •                                                       |     |

|    | 8.1  | Instances                                               | 62  |

|    | 8.2  | Configuration                                           | 63  |

|    | 8:   | 2.1 Power-On-Reset Configuration                        | 63  |

|    | _    | 2.2 Input Mode configuration                            |     |

|    |      | 2.3 Output Mode Configuration                           |     |

|    |      | · · · · · · · · · · · · · · · · · · ·                   |     |

| 8.    | .2.4 Serial Wire Debug Configuration           | 64 |

|-------|------------------------------------------------|----|

| 8.    | 2.5 GPIO Drive Strength                        | 64 |

| 8.3   | Alternate Function Configuration               | 65 |

| Q     | 3.1 Configuring GPIO (External) Interrupts     | 66 |

|       | 3.2 Using GPIO for Wakeup from Low-Power Modes |    |

| 8.4   |                                                |    |

| _     | -                                              |    |

|       | 4.1 Register Details                           |    |

| 9. St | tandard DMA (DMA)                              |    |

| 9.1   | Instances                                      | 78 |

| 9.2   | DMA Channel Operation (DMA CH)                 | 78 |

| а     | 2.1 Channel Arbitration and DMA Bursts         |    |

| _     | 2.2 Source and Destination Addressing          |    |

| _     | 2.3 Data Movement from Source to DMA           |    |

| _     | 2.4 Data Movement from DMA to Destination      |    |

| 9.3   | Usage                                          |    |

| 9.4   | Count-To-Zero (CTZ) Condition                  |    |

|       |                                                |    |

| 9.5   | Chaining Buffers                               |    |

| 9.6   | DMA Interrupts                                 |    |

| 9.7   | Channel Timeout Detect                         | 84 |

| 9.8   | Memory-to-Memory DMA                           | 85 |

| 9.9   | DMA Registers                                  | 85 |

| 9.    | 9.1 Register Details                           | 85 |

| 9.10  |                                                |    |

| 9     | 10.1 DMA Channel Register Details              | 86 |

| 10.   | UART                                           |    |

|       |                                                |    |

| 10.1  |                                                |    |

| 10.2  | UART Frame                                     | 92 |

| 10.3  | UART Interrupts                                | 93 |

| 10.4  | UART Bit Rate Calculation                      | 93 |

| 10.5  | UART DMA Using the Transmit and Receive FIFOs  | 94 |

| 10    | 0.5.1 Receive FIFO DMA Operation               | 95 |

|       | 0.5.2 Transmit FIFO DMA Operation              |    |

| 10.6  | •                                              |    |

| 10.7  | Hardware Flow Control                          | 95 |

| 10.8  |                                                |    |

|       | 0.8.1 UART Register Details                    |    |

| 11.   | Real-Time Clock (RTC)                          |    |

| 11.1  | · ,                                            |    |

| 11.1  |                                                |    |

|       |                                                |    |

| 11.3  | -3                                             |    |

|       | 1.3.1 RTC_SEC and RTC_SSEC Read Access Control |    |

| 1:    | 1.3.2 RTC Write Access Control                 |    |

| 11.4             | Alarm Functions                                  | 106 |

|------------------|--------------------------------------------------|-----|

| 11.4.1           | 1 Time-of-Day Alarm                              | 106 |

| 11.4.2           |                                                  |     |

| 11.4.3           | , , , , , , ,                                    |     |

| 11.5             | Square Wave Output                               | 108 |

| 11.6             | Calibration                                      | 108 |

| 11.7             | RTC Registers                                    | 111 |

| 11.7.1           | 1 Register Details                               | 111 |

| 12. Ti           | mers (TMR)                                       | 116 |

| 12.1             | Features                                         | 116 |

| 12.2             | Basic Operation                                  | 116 |

| 12.3             | Timer Pin Functionality                          | 117 |

| 12.4             | One-Shot Mode (0)                                | 117 |

| 12.4.1           | 1 One-Shot Mode Timer Period                     |     |

| 12.4.2           |                                                  |     |

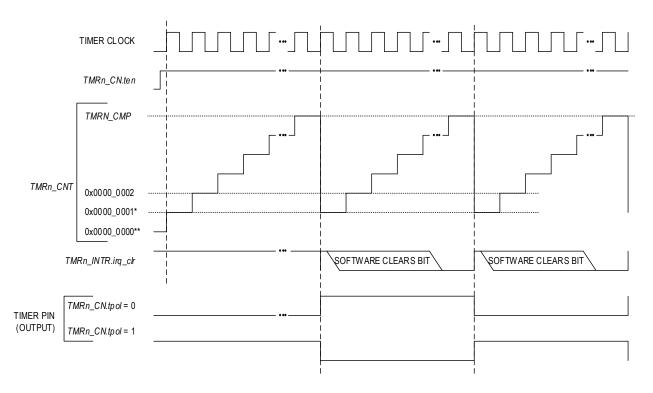

| 12.5             | Continuous Mode (1)                              | 118 |

| 12.5.1           | 1 Continuous Mode Timer Period                   | 119 |

| 12.5.2           |                                                  |     |

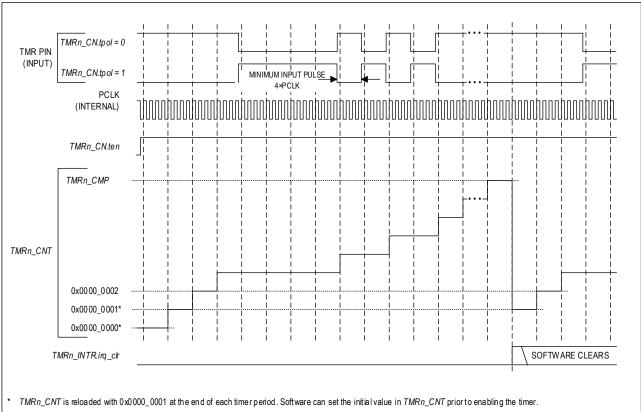

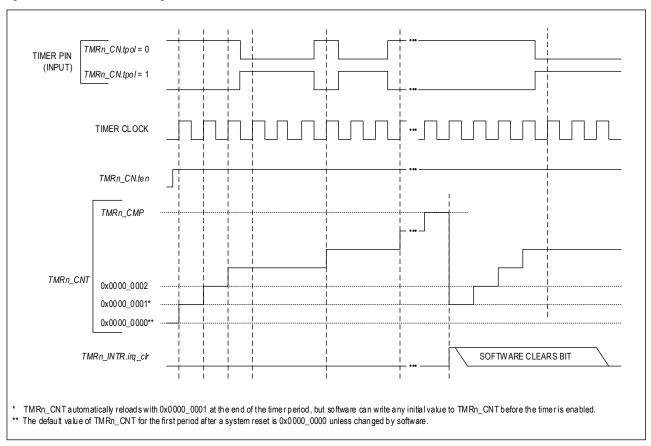

| 12.6             | Counter Mode (2)                                 |     |

| 12.6.1           | 1 Counter Mode Timer Period                      | 121 |

| 12.6.2           |                                                  |     |

| 12.7             | PWM Mode (3)                                     |     |

| 12.7.1           |                                                  |     |

| 12.7.2           |                                                  |     |

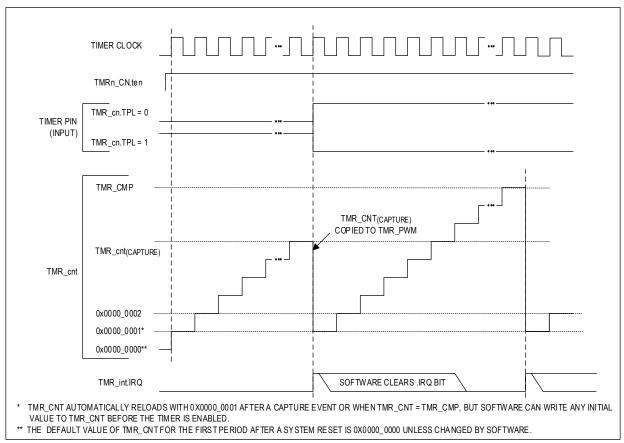

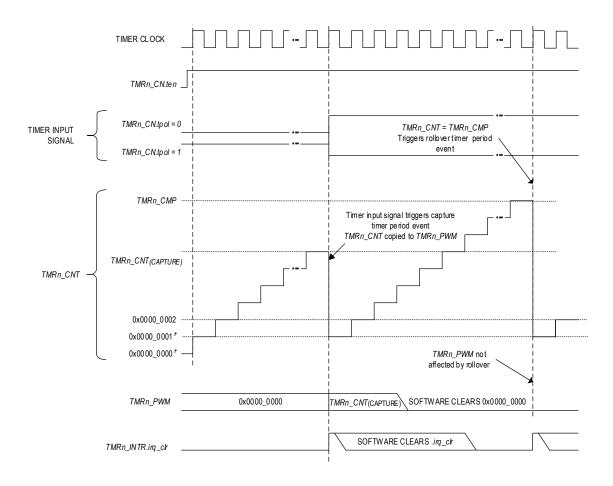

| 12.7.2           | Capture Mode (4)                                 |     |

|                  |                                                  |     |

| 12.8.1<br>12.8.2 | P                                                |     |

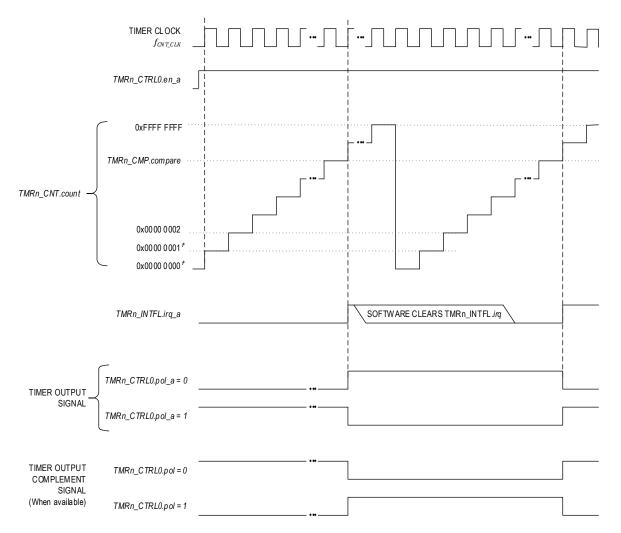

| 12.8.2           | Compare Mode (5)                                 |     |

|                  |                                                  |     |

| 12.9.1           | <b>/</b>                                         |     |

| 12.9.2<br>12.10  | 2 Compare Mode Configuration                     |     |

|                  |                                                  |     |

| 12.10            |                                                  |     |

| 12.10            | , 3                                              |     |

| 12.11            | Capture/Compare Mode (7)                         |     |

| 12.11            |                                                  |     |

| 12.11            |                                                  |     |

| 12.12            | Timer Registers                                  | 130 |

| 12.12            | .1 Register Details                              | 131 |

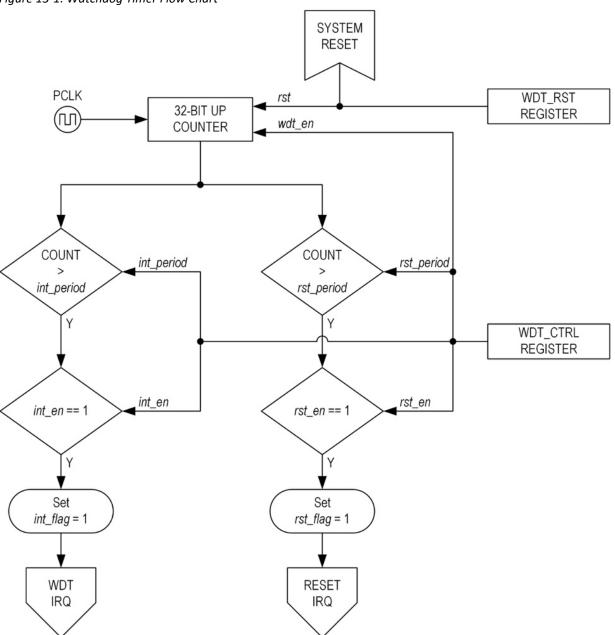

| 13. W            | /atchdog Timer (WDT)                             | 134 |

| 13.1             | Features                                         | 135 |

| 13.2             | Usage                                            | 135 |

| 13.3             | Interrupt and Reset Period Timeout Configuration | 135 |

| 13 4             | Fnabling the Watchdog Timer                      |     |

|                  |                                                  |     |

| 13.4.1 Enabling the Watchdog Timer Interrupt and Reset Functionality | 135 |

|----------------------------------------------------------------------|-----|

| 13.5 Disabling the Watchdog Timer                                    | 136 |

| 13.5.1 Manual Disable                                                | 126 |

| 13.5.2 Automatic Disable                                             |     |

| 13.6 Resetting the Watchdog Timer                                    |     |

| -                                                                    |     |

| 13.6.1 Reset Sequence                                                |     |

| 13.7 Detection of a Watchdog Reset Event                             | 136 |

| 13.8 Watchdog Timer Registers                                        | 136 |

| 13.8.1 Watchdog Timer Register Details                               | 136 |

| 14. I <sup>2</sup> C Master/Slave Serial Controller (I2C)            | 139 |

| 14.1 I <sup>2</sup> C Master/Slave Features                          | 139 |

| 14.2 Instances                                                       |     |

| _                                                                    |     |

|                                                                      |     |

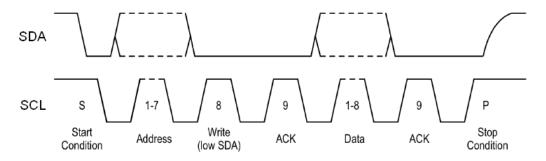

| 14.3.1 I <sup>2</sup> C Bus Terminology                              |     |

| 14.3.2 I <sup>2</sup> C Transfer Protocol Operation                  |     |

| 14.3.3 START and STOP Conditions                                     |     |

| 14.3.4 Master Operation                                              |     |

| 14.3.5 Acknowledge and Not Acknowledge                               |     |

| 14.3.6 Bit Transfer Process                                          |     |

| 14.4 Configuration and Usage                                         | 141 |

| 14.4.1 SCL and SDA Bus Drivers                                       | 141 |

| 14.4.2 SCL Clock Configurations                                      | 142 |

| 14.4.3 SCL Clock Generation for Standard, Fast and Fast-Plus Modes   | 142 |

| 14.4.4 SCL Clock Generation for Hs-mode                              | 143 |

| 14.4.5 Addressing                                                    | 144 |

| 14.4.6 Master Mode Operation                                         | 144 |

| 14.4.7 Slave Mode Operation                                          | 147 |

| 14.4.8 Interrupt Sources                                             |     |

| 14.4.9 Transmit FIFO and Receive FIFO                                |     |

| 14.4.10 Transmit FIFO Preloading                                     |     |

| 14.4.11 Interactive Receive Mode (IRXM)                              |     |

| 14.4.12 Clock Stretching                                             |     |

| 14.4.13 Bus Timeout                                                  |     |

| 14.4.14 DMA Control                                                  |     |

| 14.5 I <sup>2</sup> C Registers                                      |     |

| 14.5.1 Register Details                                              | 157 |

| 15. Serial Peripheral Interface (SPI): SPI0 (SPI17Y)                 |     |

|                                                                      |     |

| 15.1 Instances                                                       |     |

| 15.2 Formats                                                         | 172 |

| 15.2.1 Four-Wire SPI                                                 |     |

| 15.2.2 Three-Wire SPI                                                |     |

| 15.3 Pin Configuration                                               | 174 |

| 15.3.1 SPIO Alternate Function Mapping                               | 174 |

| 15.3.2 Four-Wire Format Configuration                                | 174 |

| 15.3.3 Three-Wire Format Configuration                               | 174 |

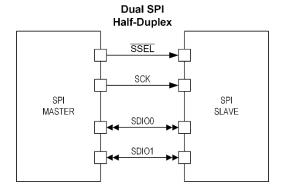

| 15.3.4 Dual-Mode Format Configuration                                | 175 |

| 15.4 Clock Configuration                                             | 175 |

| 15.4.1 Serial Clock                          | 175 |

|----------------------------------------------|-----|

| 15.4.2 Peripheral Clock                      | 175 |

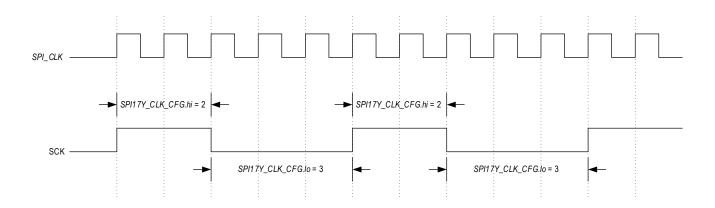

| 15.4.3 Master Mode Serial Clock Generation   | 176 |

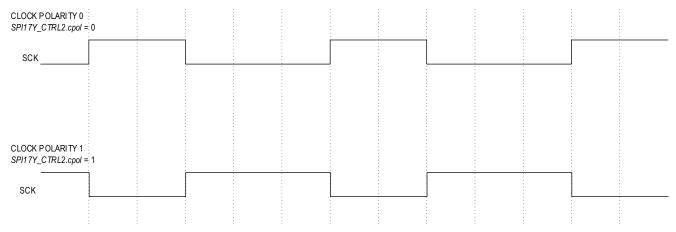

| 15.4.4 Clock Phase and Polarity Control      | 176 |

| 15.4.5 Transmit and Receive FIFOs            | 177 |

| 15.4.6 Interrupts and Wakeups                | 177 |

| 15.5 SPIO Registers                          | 178 |

| 15.5.1 Register Details                      |     |

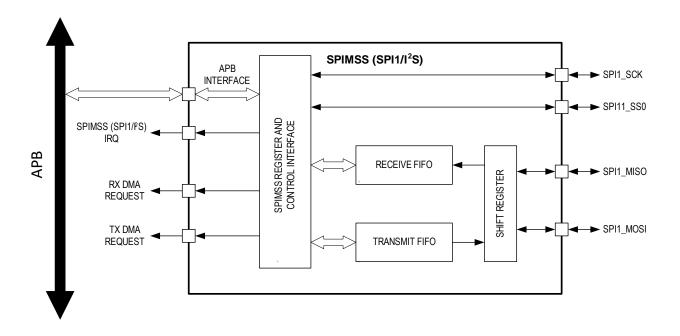

| 16. SPIMSS (SPI1/I <sup>2</sup> S)           |     |

| 16.1.1 Features                              | 188 |

| 16.2 Pin Configuration                       | 189 |

| 16.3 I <sup>2</sup> S System                 | 190 |

| 16.4 SPIMSS Clock Phase and Polarity Control | 190 |

| 16.5 Data Movement                           | 191 |

| 16.6 I <sup>2</sup> S (Inter-IC Sound) Mode  | 191 |

| 16.6.1 Mute                                  | 192 |

| 16.6.2 Pause                                 | 192 |

| 16.6.3 Mono                                  | 192 |

| 16.6.4 Right and Left Justify                | 192 |

| 16.7 Error Detection                         | 193 |

| 16.7.1 Transmit Overrun                      |     |

| 16.7.2 Transmit Underrun                     |     |

| 16.7.3 Mode Fault (Multi-Master Collision)   |     |

| 16.7.4 Slave Mode Abort                      | 193 |

| 16.7.5 Receive Overrun                       | 194 |

| 16.8 SPIMSS Interrupts                       | 194 |

| 16.8.1 Data Interrupt                        | 194 |

| 16.8.2 Forced Interrupt                      | 194 |

| 16.8.3 Error Condition Interrupt             | 194 |

| 16.8.4 Bit Rate Generator Timeout Interrupt  | 194 |

| 16.9 SPIMSS Bit Rate Generator               | 194 |

| 16.9.1 Slave Mode                            |     |

| 16.9.2 Master Mode                           |     |

| 16.9.3 Timer Mode                            |     |

| 16.10 SPIMSS Registers                       | 195 |

| 16.10.1 Register Details                     |     |

| 17. Revision History                         | 201 |

# **Table of Tables**

| Table 1-1: Field Access Definitions                                                                         | 14 |

|-------------------------------------------------------------------------------------------------------------|----|

| Table 1-2: Example Registers                                                                                | 15 |

| Table 1-3: Name 0 Register                                                                                  | 15 |

| Table 3-1: APB Peripheral Base Address Map                                                                  | 23 |

| Table 4-1: OVR Selection and the Effect on V <sub>CORE</sub> and SYS_OSC                                    | 24 |

| Table 4-2: Minimum Flash Wait State Setting for Each OVR Setting (fsysclk = fhfio)                          |    |

| Table 4-3: Minimum Flash Wait State Setting for Each OVR Setting (f <sub>SYSCLK</sub> = f <sub>NANO</sub> ) |    |

| Table 4-4: Minimum Flash Wait State Setting for Each OVR Setting (fsysclk = fx32k)                          |    |

| Table 4-5: Reset Sources and Effect on Oscillator Status                                                    |    |

| Table 4-6: Reset Sources and Effect on System Oscillator Selection and Prescaler                            |    |

| Table 4-7: Wakeup Sources                                                                                   |    |

| Table 4-8: Types of Resets and the Effects on Each Clock Source and the Global Control Registers            |    |

| Table 4-9: Low-Power Modes and the Effects on Each Clock Source and the Global Control Registers            |    |

| Table 4-10: Types of Resets and the Effects on Each Clock Source and the Global Control Registers           |    |

| Table 4-11: Low-Power Modes and the Effects on the CPU, Peripherals and Power Domains                       |    |

| Table 4-12: ICC Registers                                                                                   |    |

| Table 4-13: ICC Cache ID Register                                                                           |    |

| Table 4-14: ICC Memory Size Register                                                                        |    |

| Table 4-15: ICC Cache Control Register                                                                      |    |

| Table 4-16: ICC Invalidate Register                                                                         |    |

| Table 4-17: System RAM Banks, Size and Base Address                                                         |    |

| Table 4-18: Global Control Registers                                                                        |    |

| Table 4-19: System Control Register                                                                         |    |

| Table 4-20: Reset 0 Register                                                                                |    |

| Table 4-21: System Clock Control Register                                                                   |    |

|                                                                                                             |    |

| Table 4-22: Power Management Register                                                                       |    |

| Table 4-23: Peripheral Clock Divisor Register                                                               |    |

| Table 4-24: Peripheral Clock Disable 0 Register                                                             |    |

| Table 4-25: Memory Clock Control Register                                                                   |    |

| Table 4-26: Memory Zeroization Control Register                                                             |    |

| Table 4-27: SCCK Register                                                                                   |    |

| Table 4-28: MPRIO Register                                                                                  |    |

| Table 4-29: MPRI1 Register                                                                                  |    |

| Table 4-30: System Status Flag Register                                                                     |    |

| Table 4-31: Reset Register 1                                                                                |    |

| Table 4-32: Peripheral Clock Disable Register 1                                                             |    |

| Table 4-33: Event Enable Register                                                                           |    |

| Table 4-34: Revision Register                                                                               |    |

| Table 4-35: System Status Interrupt Enable Register                                                         |    |

| Table 4-36: System Initialization Registers                                                                 |    |

| Table 4-37: Function Control Register 0                                                                     | 46 |

| Table 4-38: System Initialization Address Error Register                                                    | 47 |

| Table 4-39: System Initialization Function Status Register                                                  | 47 |

| Table 4-40: System Initialization Function Status Register                                                  | 47 |

| Table 4-41: Power Sequencer Low-Power Control Registers                                                     | 48 |

| Table 4-42: Low-Power Voltage Control Register                                                              | 48 |

| Table 4-43: Low-Power Mode Wakeup Flags for GPIO0                                                           | 50 |

| Table 4-44: Low-Power Wakeup Enable for GPIOO Register                                                      |    |

| Table 4-45: RAM Shut Down Register                                                                          |    |

| Table 5-1: MAX32660 Interrupt Vector Table                                                                  |    |

| Table 6-1: MAX32660 DAP Instance                                         |    |

|--------------------------------------------------------------------------|----|

| Table 7-1: Internal Flash Memory Organization                            |    |

| Table 7-2: Valid Addresses for 32-bit and 128-bit Internal Flash Writes  | 56 |

| Table 7-3: Flash Controller Registers                                    |    |

| Table 7-4: Flash Controller Interrupt Register                           |    |

| Table 7-5: Flash Controller Data Register 0                              | 60 |

| Table 7-6: Flash Controller Data Register 1                              |    |

| Table 7-7: Flash Controller Data Register 2                              | 60 |

| Table 7-8: Flash Controller Data Register 3                              | 60 |

| Table 7-9: Flash Controller Access Control Register                      | 61 |

| Table 8-1: GPIO Pin Count                                                | 62 |

| Table 8-2: MAX32660 Input Mode Configuration Summary                     | 63 |

| Table 8-3: Standard GPIO Drive Strength Selection                        | 64 |

| Table 8-4: GPIO with I <sup>2</sup> C AF Drive Strength Selection        | 65 |

| Table 8-5: GPIO Mode and AF Selection                                    | 65 |

| Table 8-6: GPIO Mode and AF Transition Selection                         | 65 |

| Table 8-7: GPIO AF Configuration Reference                               | 65 |

| Table 8-8: GPIO Wakeup Interrupt Vector                                  | 66 |

| Table 8-9: GPIO Register Summary                                         | 67 |

| Table 8-10: GPIO AF 0 Select Register                                    | 68 |

| Table 8-11: GPIO Port n Configuration Enable Atomic Set Bit 0 Register   | 68 |

| Table 8-12: GPIO Port n Configuration Enable Atomic Clear Bit 0 Register | 68 |

| Table 8-13: GPIO Port n Output Enable Register                           | 68 |

| Table 8-14: GPIO Port n Output Enable Atomic Set Register                | 69 |

| Table 8-15: GPIO Port n Output Enable Atomic Clear Register              |    |

| Table 8-16: GPIO Port n Output Register                                  |    |

| Table 8-17: GPIO Port n Output Atomic Set Register                       | 69 |

| Table 8-18: GPIO Port n Output Atomic Clear Register                     |    |

| Table 8-19: GPIO Port n Input Register                                   |    |

| Table 8-20: GPIO Port n Interrupt Mode Register                          |    |

| Table 8-21: GPIO Port n Interrupt Polarity Register                      |    |

| Table 8-22: GPIO Port n Interrupt Enable Registers                       |    |

| Table 8-23: GPIO Port n Interrupt Enable Atomic Set Register             |    |

| Table 8-24: GPIO Port n Interrupt Enable Atomic Clear Register           |    |

| Table 8-25: GPIO Interrupt Status Register                               | 71 |

| Table 8-26: GPIO Port n Interrupt Clear Register                         |    |

| Table 8-27: GPIO Port n Wakeup Enable Register                           |    |

| Table 8-28: GPIO Port n Wakeup Enable Atomic Set Register                |    |

| Table 8-29: GPIO Port n Wakeup Enable Atomic Clear Register              |    |

| Table 8-30: GPIO Port n Interrupt Dual Edge Mode Register                |    |

| Table 8-31: GPIO Port n Pad Control 0 Register                           |    |

| Table 8-32: GPIO Port n Pad Control 1 Register                           |    |

| Table 8-33: GPIO Port n Configuration Enable Bit 1 Register              |    |

| Table 8-34: GPIO Port n Configuration Enable Atomic Set Bit 1 Register   |    |

| Table 8-35: GPIO Port n Configuration Enable Atomic Clear Bit 1 Register |    |

| Table 8-36: GPIO Port n Configuration Enable Bit 2 Register              |    |

| Table 8-37: GPIO Port n Configuration Enable Atomic Set Bit 2 Register   |    |

| Table 8-38: GPIO Port n Configuration Enable Atomic Clear Bit 2 Register |    |

| Table 8-39: GPIO Port n Input Hysteresis Enable Register                 |    |

| Table 8-40: GPIO Port n Slew Rate Enable Register                        |    |

| Table 8-41: GPIO Port n Output Drive Strength Bit 0 Register             |    |

| Table 8-42: GPIO Port n Output Drive Strength Bit 1 Register             |    |

| Table 8-43: GPIO Port in Pulldown/Pullun Strength Select Register        | 76 |

| Table 8-44: GPIO Port n Voltage Select Register                              | 77  |

|------------------------------------------------------------------------------|-----|

| Table 9-1: MAX32660 DMA and Channel Instances                                |     |

| Table 9-2: DMA Source and Destination by Peripheral                          |     |

| Table 9-3: Data Movement from Source to DMA FIFO                             |     |

| Table 9-4: Data Movement from the DMA FIFO to Destination                    |     |

| Table 9-5: DMA Channel Timeout Configuration                                 |     |

| Table 9-6: DMA Register Summary                                              |     |

| Table 9-7: DMA Interrupt Flag Register                                       |     |

| Table 9-8: DMA Interrupt Enable Register                                     |     |

| Table 9-9: Standard DMA Channel 0 to Channel 3 Register Summary              |     |

| Table 9-10: DMA Channel Registers Summary                                    |     |

| Table 9-11: DMA CH n Control Register                                        |     |

| Table 9-12: DMA Status Register                                              |     |

| Table 9-13: DMA Channel n Source Register                                    |     |

| Table 9-14: DMA Channel n Destination Register                               |     |

| Table 9-15: DMA Channel n Count Register                                     |     |

| Table 9-16: DMA Channel n Source Reload Register                             |     |

| Table 9-17: DMA Channel n Destination Reload Register                        |     |

| Table 9-18: DMA Channel n Count Reload Register                              |     |

| Table 10-1: MAX32660 UART Instances                                          |     |

| Table 10-1: MAX32000 GART Instances                                          |     |

| Table 10-3: Example Baud Rate Calculation Results, Target Bit Rate = 1.8Mbps |     |

| Table 10-4. UART Register Offsets, Names, Access and Descriptions            |     |

| Table 10-5: UART Control 0 Register                                          |     |

| Table 10-5: UART Threshold Control 1 Register                                |     |

| Table 10-7: UART Status Register                                             |     |

| Table 10-7: UART Interrupt Enable Register                                   |     |

| Table 10-9: UART Interrupt Flags Register                                    |     |

|                                                                              |     |

| Table 10-10: UART Rate Integer Register                                      |     |

| Table 10-11: UART Baud Rate Decimal Register                                 |     |

| Table 10-12: UART FIFO Register                                              |     |

| Table 10-13: UART DMA Configuration Register                                 |     |

| Table 10-14: UART Transmit FIFO Data Output Register                         |     |

| Table 11-1: MAX32660 RTC Counter and Alarm Registers                         |     |

| Table 11-2: RTC Register Access                                              |     |

| Table 11-3: MAX32660 RTC Square Wave Output Configuration                    |     |

| Table 11-4: RTC Register Summary                                             |     |

| Table 11-5: RTC Seconds Counter Register                                     |     |

| Table 11-6: RTC Sub-Second Counter Register                                  |     |

| Table 11-7: RTC Time-of-Day Alarm Register                                   |     |

| Table 11-8: RTC Sub-Second Alarm Register                                    |     |

| Table 11-9: RTC Control Register                                             |     |

| Table 11-10: RTC Trim Register                                               |     |

| Table 11-11: RTC 32kHz Oscillator Control Register                           |     |

| Table 12-1: Timer Register Summary                                           |     |

| Table 12-2: Timer Count Registers                                            |     |

| Table 12-3: Timer Compare Registers                                          |     |

| Table 12-4: Timer PWM Registers                                              |     |

| Table 12-5: Timer Interrupt Registers                                        |     |

| Table 12-6: Timer Control Registers                                          |     |

| Table 12-7: Timer Non-Overlapping Compare Register                           |     |

| Table 13-1: Watchdog Timer Register Offsets, Names and Descriptions          |     |

| Table 13-2: Watchdog Timer Control Register                                  | 136 |

| Table 13-3: Watchdog Timer Reset Register                        | 138 |

|------------------------------------------------------------------|-----|

| Table 14-1: MAX32660 I <sup>2</sup> C Peripheral Pins            | 139 |

| Table 14-2: I <sup>2</sup> C Bus Terminology                     | 140 |

| Table 14-3: Calculated I <sup>2</sup> C Bus Clock Frequencies    | 143 |

| Table 14-4: I <sup>2</sup> C Slave Address Format                | 144 |

| Table 14-5: I <sup>2</sup> C Registers                           | 156 |

| Table 14-6: I <sup>2</sup> C Control Register                    | 157 |

| Table 14-7: I <sup>2</sup> C Status Registers                    | 158 |

| Table 14-8: I <sup>2</sup> C Interrupt Status Flags Registers 0  | 160 |

| Table 14-9: I <sup>2</sup> C Interrupt Enable 0 Registers        | 161 |

| Table 14-10: I <sup>2</sup> C Interrupt Status Flags 1 Registers | 163 |

| Table 14-11: I <sup>2</sup> C Interrupt Enable Registers 1       | 163 |

| Table 14-12: I <sup>2</sup> C FIFO Length Registers              | 164 |

| Table 14-13: I <sup>2</sup> C Receive Control Registers 0        | 164 |

| Table 14-14: I <sup>2</sup> C Receive Control 1 Registers        | 165 |

| Table 14-15: I <sup>2</sup> C Transmit Control Registers 0       | 165 |

| Table 14-16: I <sup>2</sup> C Transmit Control Registers 1       | 166 |

| Table 14-17: I <sup>2</sup> C Data Registers                     | 166 |

| Table 14-18: I <sup>2</sup> C Master Mode Control Registers      | 166 |

| Table 14-19: I <sup>2</sup> C SCL Low Control Register           | 167 |

| Table 14-20: I <sup>2</sup> C SCL High Control Register          | 167 |

| Table 14-21: I <sup>2</sup> C Timeout Registers                  | 167 |

| Table 14-22: I <sup>2</sup> C Timeout Registers                  |     |

| Table 14-23: I <sup>2</sup> C Slave Address Register             |     |

| Table 14-24: I <sup>2</sup> C DMA Register                       | 168 |

| Table 15-1: SPIO Instances                                       |     |

| Table 15-2: SPIO Peripheral Pins                                 | 172 |

| Table 15-3: Four-Wire Format Signals                             |     |

| Table 15-4: Three-Wire Format Signals                            |     |

| Table 15-5: SPI Modes Clock Phase and Polarity Operation         |     |

| Table 15-6: SPIO Master Register Addresses and Descriptions      |     |

| Table 15-7: SPI0 FIFO32 Register                                 |     |

| Table 15-8: SPI0 16-bit FIFO Register                            |     |

| Table 15-9: SPIO 8-bit FIFO Register                             |     |

| Table 15-10: SPIO Control 0 Register                             |     |

| Table 15-11: SPIO Control 1 Register                             |     |

| Table 15-12: SPIO Control 2 Register                             |     |

| Table 15-13: SPIO Slave Select Timing Register                   |     |

| Table 15-14: SPIO Master Clock Configuration Registers           |     |

| Table 15-15: SPIO DMA Control Registers                          |     |

| Table 15-16: SPIO Interrupt Status Flags Registers               |     |

| Table 15-17: SPIO Interrupt Enable Registers                     |     |

| Table 15-18: SPIO Wakeup Status Flags Registers                  |     |

| Table 15-19: SPIO Wakeup Enable Registers                        |     |

| Table 15-20: SPIO Slave Select Timing Registers                  |     |

| Table 16-1: SPIMSS (SPI1/I <sup>2</sup> S) Pins                  |     |

| Table 16-2: Clock Phase and Polarity Operation                   |     |

| Table 16-3: SPIMSS Register Offsets, Access and Descriptions     |     |

| Table 16-4: SPIMSS Data Register                                 |     |

| Table 16-5: SPIMSS Control Register                              |     |

| Table 16-6: SPIMSS Interrupt Flag Register                       |     |

| Table 16-7: SPIMSS Mode Register                                 |     |

| Table 16-8: SPIMSS Bit Rate Generator Register                   |     |

## MAX32660 User Guide

| Table 16-9: SPIMSS DMA Register                       | 198  |

|-------------------------------------------------------|------|

| Table 16-10: SPIMSS I <sup>2</sup> S Control Register |      |

| Table 17-1: Revision History                          |      |

| I abie 17-1. Revision filstory                        | ۷0 . |

# **Table of Figures**

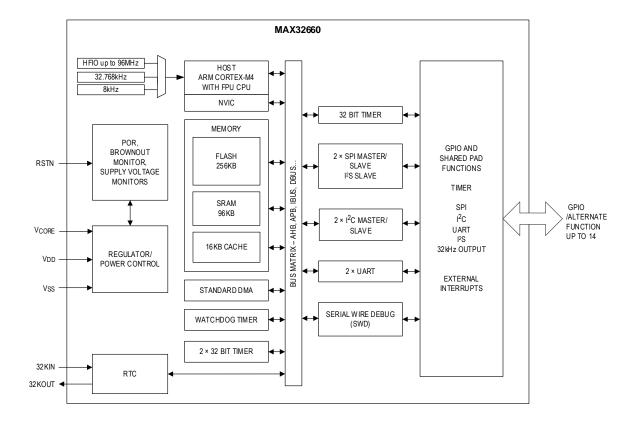

| Figure 2-1: MAX32660 High-Level Block Diagram                                   | 16  |

|---------------------------------------------------------------------------------|-----|

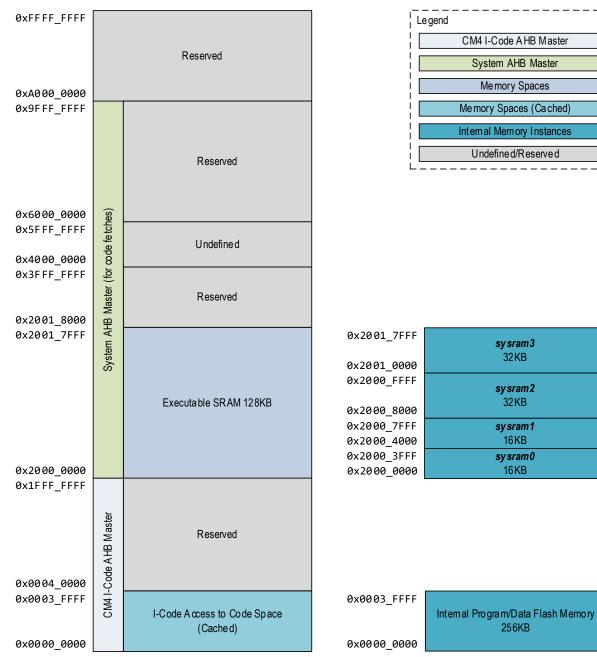

| Figure 3-1: Code Memory Mapping                                                 | 18  |

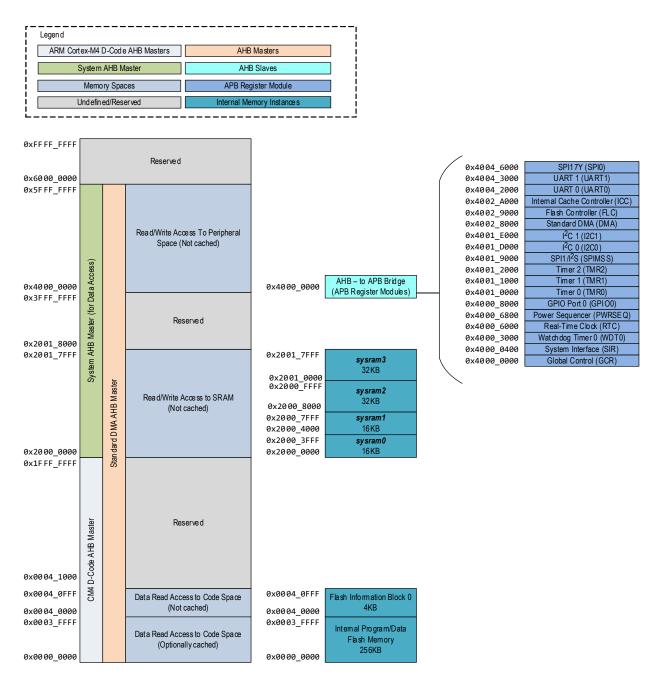

| Figure 3-2: Data Memory Map                                                     | 19  |

| Figure 3-3: Unique Serial Number Format                                         | 22  |

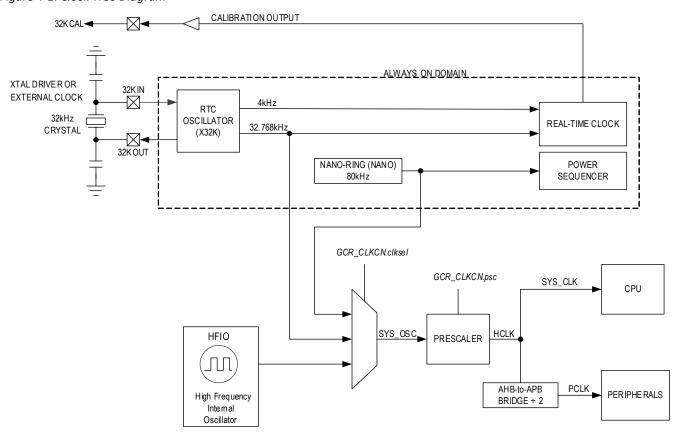

| Figure 4-1: Clock Tree Diagram                                                  | 28  |

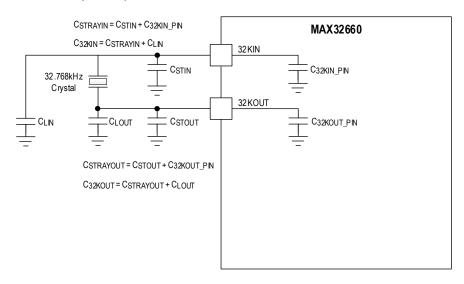

| Figure 4-2: Example 32.768kHz Crystal Capacitor Determination                   | 29  |

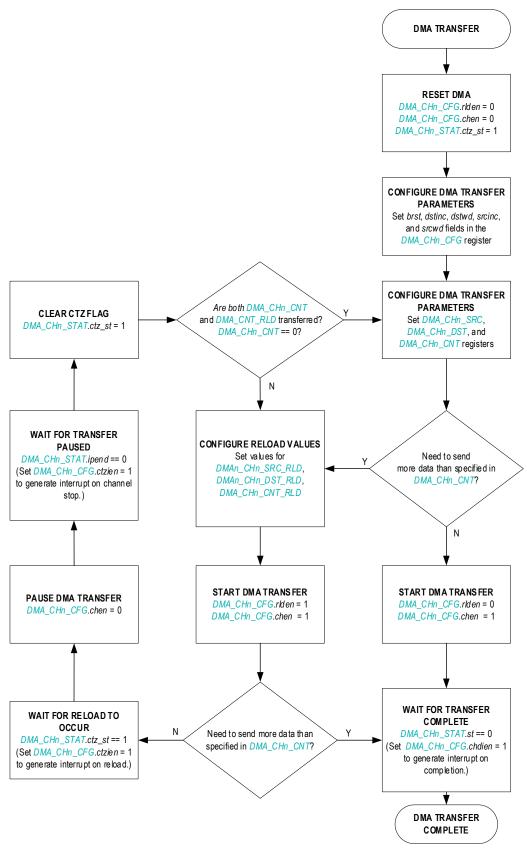

| Figure 9-1: DMA Block-Chaining Flowchart                                        | 83  |

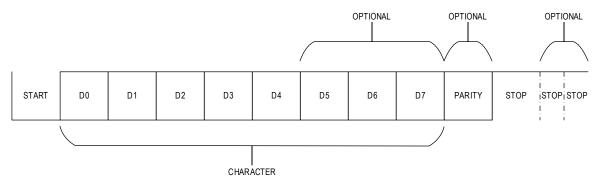

| Figure 10-1: UART Frame Diagram                                                 | 92  |

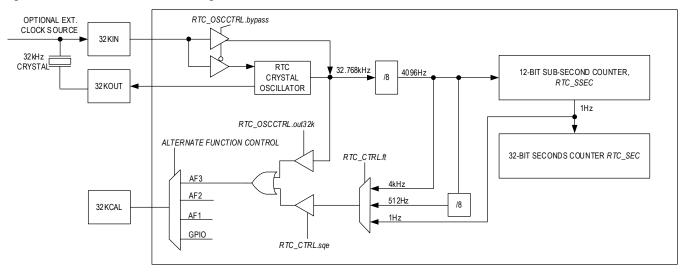

| Figure 11-1: MAX32660 RTC Block Diagram                                         | 104 |

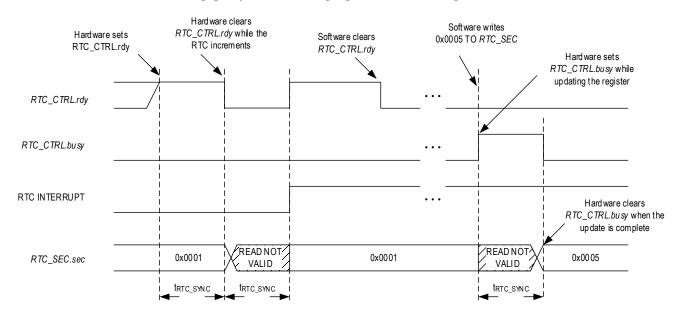

| Figure 11-2: Busy/Ready Signal Timing Example for the RTC_SEC.sec Field         | 106 |

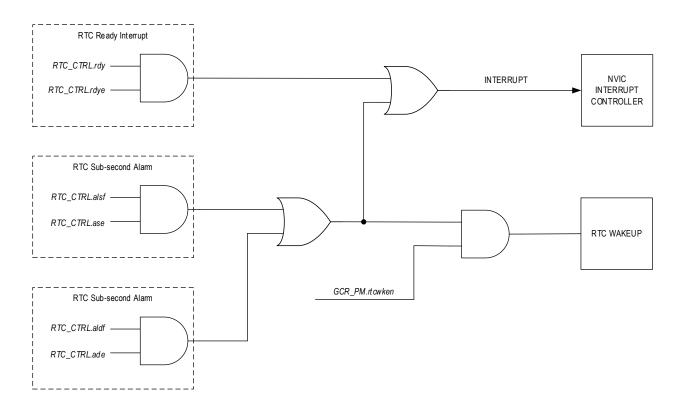

| Figure 11-3: RTC Interrupt/Wakeup Diagram                                       | 107 |

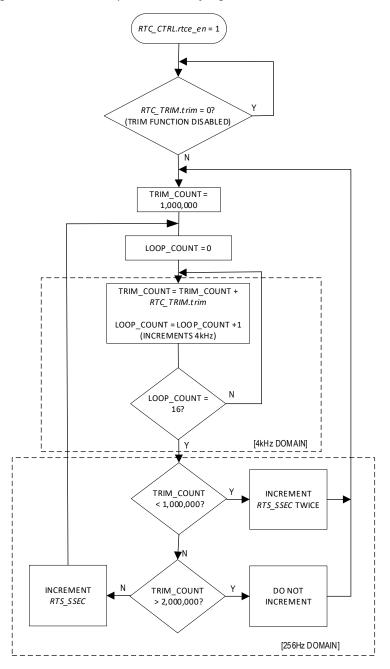

| Figure 11-4: Internal Implementation of Digital Trim                            | 109 |

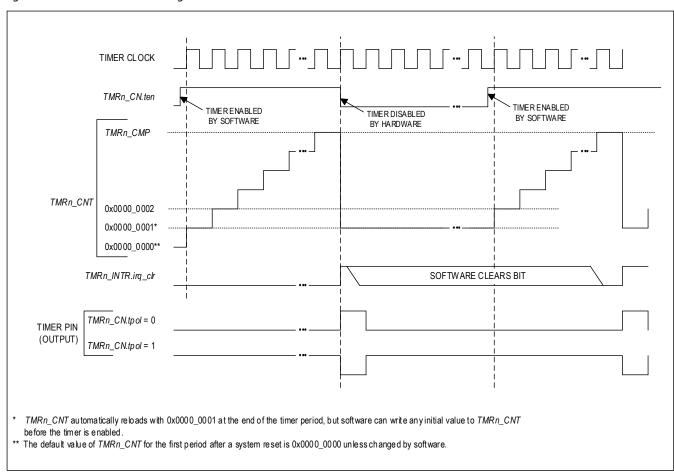

| Figure 12-1: One-Shot Mode Diagram                                              | 117 |

| Figure 12-2: Continuous Mode Diagram                                            | 119 |

| Figure 12-3: Counter Mode Diagram                                               | 120 |

| Figure 12-4: Capture Mode Diagram                                               | 123 |

| Figure 12-5: Compare Mode Diagram                                               | 125 |

| Figure 12-6: Gated Mode Diagram                                                 | 127 |

| Figure 12-7: Capture/Compare Mode Diagram                                       | 129 |

| Figure 13-1: Watchdog Timer Flow Chart                                          | 134 |

| Figure 14-1: I <sup>2</sup> C Write Data Transfer                               | 141 |

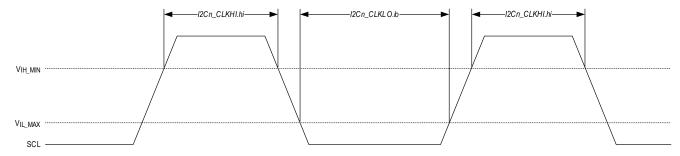

| Figure 14-2: I <sup>2</sup> C SCL Timing for Standard, Fast and Fast-Plus Modes | 142 |

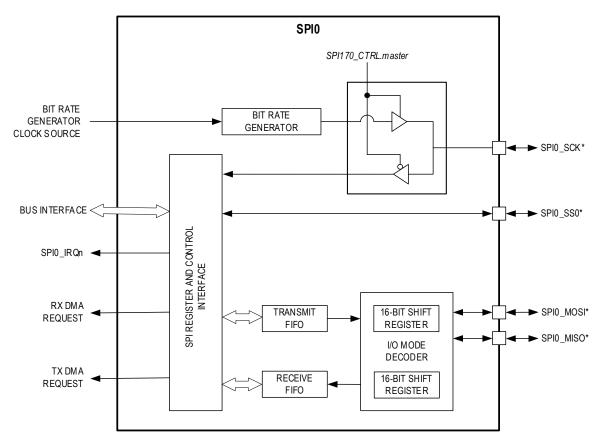

| Figure 15-1: SPIO Block Diagram                                                 | 171 |

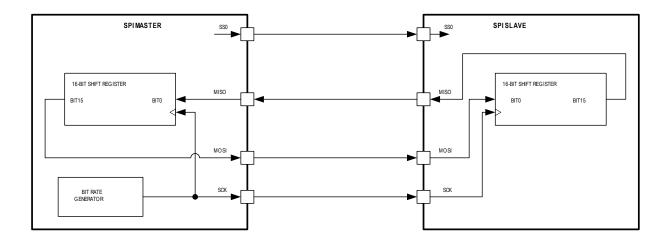

| Figure 15-2: 4-Wire SPI Connection Diagram                                      | 173 |

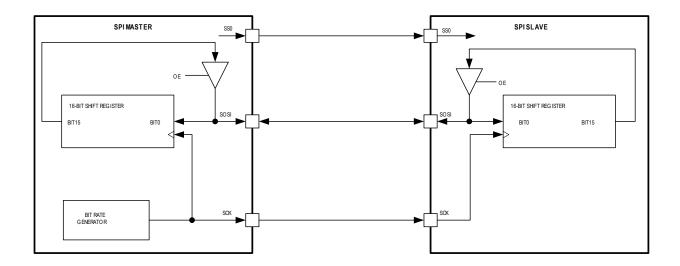

| Figure 15-3: Generic 3-Wire SPI Master to Slave Connection                      | 174 |

| Figure 15-4: Dual Mode SPI Connection Diagram                                   | 175 |

| Figure 15-5: SCK Clock Rate Control                                             | 176 |

| Figure 15-6: SPI Clock Polarity                                                 | 177 |

| Figure 16-1: SPIMSS Block Diagram                                               | 189 |

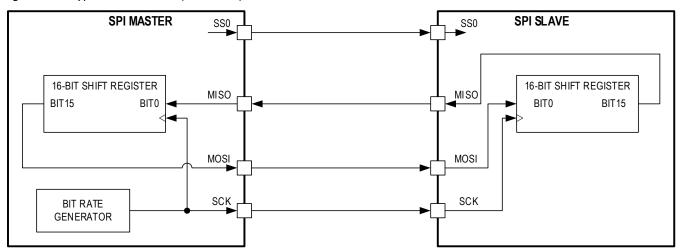

| Figure 16-2: Typical SPI Network (Four-Wire)                                    | 189 |

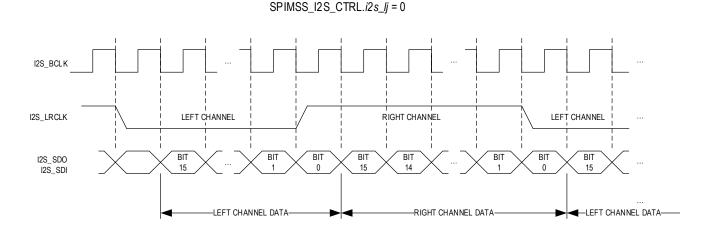

| Figure 16-3: I <sup>2</sup> S Mode Right Justify Mode                           | 192 |

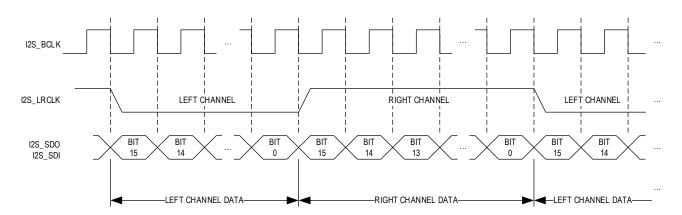

| Figure 16-4: I <sup>2</sup> S Mode Left Justify Mode                            |     |

# **Table of Equations**

| Equation 4-1: System Clock Scaling                                                                                           | 27  |

|------------------------------------------------------------------------------------------------------------------------------|-----|

| Equation 4-2: AHB Clock                                                                                                      | 27  |

| Equation 4-3: APB Clock                                                                                                      | 27  |

| Equation 4-4: Always-on Domain (AoD) Clock                                                                                   | 27  |

| Equation 4-5: Determining Load Capacitance for X32K                                                                          | 29  |

| Equation 7-1: FLC Clock Frequency                                                                                            | 55  |

| Equation 10-1: UART Bit Rate Divisor Equation                                                                                | 93  |

| Equation 10-2: Bit Rate Integer Calculation                                                                                  | 94  |

| Equation 10-3: Bit Rate Remainder Calculation                                                                                | 94  |

| Equation 12-1: Timer Peripheral Clock Equation                                                                               | 116 |

| Equation 12-2: One-shot Mode Timer Period                                                                                    | 118 |

| Equation 12-3: Continuous Mode Timer Period                                                                                  | 120 |

| Equation 12-4: Counter Mode Frequency/Input Pulse Width                                                                      | 120 |

| Equation 12-5: Counter Mode Timer Input Transitions                                                                          | 121 |

| Equation 12-6: Timer PWM Period                                                                                              | 122 |

| Equation 12-7: Timer PWM Output High Time Ratio with Polarity 0                                                              | 122 |

| Equation 12-8: Timer PWM Output High Time Ratio with Polarity 1                                                              | 122 |

| Equation 12-9: Capture Mode Elapsed Time Calculation in Seconds                                                              | 124 |

| Equation 12-10: Compare Mode Timer Period                                                                                    | 126 |

| Equation 12-11: Capture Mode Elapsed Time                                                                                    | 130 |

| Equation 13-1: Watchdog Timer Interrupt Period                                                                               | 135 |

| Equation 13-2: Watchdog Timer Reset Period                                                                                   | 135 |

| Equation 14-1: I <sup>2</sup> C Clock Frequency                                                                              | 142 |

| Equation 14-2: I <sup>2</sup> C Clock High Time Calculation                                                                  | 142 |

| Equation 14-3: I <sup>2</sup> C Clock Low Time Calculation                                                                   | 142 |

| Equation 14-4: I <sup>2</sup> C Target SCL Frequency                                                                         | 143 |

| Equation 14-5: Determining the I2Cn_HS_CLK.hsclk_lo Register Value                                                           | 143 |

| Equation 14-6: Determining the I2Cn_HS_CLK.hsclk_hi Register Value                                                           | 143 |

| Equation 14-7: The Calculated Frequency of the $I^2C$ Bus Clock Using the Results of Equation 14-5 and Equation 14-6 $\dots$ | 143 |

| Equation 14-8: I <sup>2</sup> C Timeout Maximum                                                                              | 155 |

| Equation 14-9: I <sup>2</sup> C Timeout Minimum                                                                              | 155 |

| Equation 14-10: DMA Burst Size Calculation for I <sup>2</sup> C Transmit                                                     | 155 |

| Equation 14-11: DMA Burst Size Calculation for I <sup>2</sup> C Receive                                                      | 156 |

| Equation 15-1: SPI Peripheral Clock                                                                                          | 175 |

| Equation 15-2: SCK High Time                                                                                                 | 176 |

| Equation 15-3: SCK Low Time                                                                                                  | 176 |

| Equation 16-1: SPIMSS Bit Rate Equation                                                                                      | 195 |

# 1. Introduction

For ordering information, mechanical and electrical characteristics for the MAX32660 family of devices, please refer to the datasheet. For information on the Arm® Cortex®-M4 with FPU core, please refer to the Arm Cortex-M4 Processor Technical Reference Manual.

## 1.1 Related Documentation

The MAX32660 datasheet and errata are available from the Maxim Integrated® website, <a href="http://www.maximintegrated.com/MAX32660">http://www.maximintegrated.com/MAX32660</a>.

# 1.2 Conventions Used in this Document

## 1.2.1 Number Notations

| Notation | Description                                                                                                        |

|----------|--------------------------------------------------------------------------------------------------------------------|

| 0xNN     | Hexadecimal (Base 16) numbers are preceded by the prefix 0x.                                                       |

| 0bNN     | Binary (Base 2) numbers are preceded by the prefix 0b.                                                             |

| NN       | Decimal (Base 10) numbers are represented using no additional prefix or suffix.                                    |

| V[X:Y]   | Bit field representation of a register, field, or value (V) covering Bit X to Bit Y.                               |

| Bit N    | Bits are numbered in little-endian format; that is, the least significant bit of a number is referred to as Bit 0. |

| [0xNNNN] | An address offset from a base address is shown in bracket form.                                                    |

# 1.2.2 Register and Field Access Definitions

All the fields that are accessible by user software have distinct access capabilities. Each register table contained in this user guide has an access type defined for each field. The definition of each field access type is presented in *Table 1-1*.

Table 1-1: Field Access Definitions

| Access Type | Definition                                                                                                                                                     |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RO          | Reserved This access type is reserved for static fields. Reads of this field return the reset value. Writes are ignored.                                       |

| DNM         | Reserved. Do Not Modify Software must first read this field and write the same value whenever writing to this register.                                        |

| R           | Read Only Reads of this field return a value. Writes to the field do not affect device operation.                                                              |

| W           | Write Only Reads of this field return indeterminate values. Writes to the field change the field's state to the value written and can affect device operation. |

| R/W         | Unrestricted Read/Write Reads of this field return a value. Writes to the field change the field's state to the value written and can affect device operation. |

| RC          | Read to Clear Reading this field clears the field to 0. Writes to the field do not affect device operation.                                                    |

| RS          | Read to Set Reading this field sets the field to 1. Writes to the field do not affect device operation.                                                        |

| R/W0        | Read/Write 0 Only Writing 0 to this field set the field to 0. Writing 1 to the field does not affect device operation.                                         |

Maxim Integrated Page 14 of 201

| Access Type | Definition                                                                                                                     |

|-------------|--------------------------------------------------------------------------------------------------------------------------------|

| R/W1        | Read/Write 1 Only Writing 1 to this field sets the field to 1. Writing 0 to the field does not affect device operation.        |

| R/W1C       | Read/Write 1 to Clear Writing 1 to this field clears this field to 0. Writing 0 to the field does not affect device operation. |

| R/W0S       | Read/Write 0 to Set Writing 0 to this field sets this field to 1. Writing 1 to the field does not affect device operation.     |

# 1.2.3 Register Lists

Each peripheral includes a table listing all of the peripheral's registers. The register table includes the offset, register name, and description of each register. The offset shown in the table must be added to the peripheral's base address in *Table 3-1* to get the register's absolute address.

Table 1-2: Example Registers

| Offset   | Register Name | Description     |

|----------|---------------|-----------------|

| [0x0000] | REG_NAME0     | Name 0 Register |

# 1.2.4 Register Detail Tables

Each register in a peripheral includes a detailed register table, as shown in *Table 1-3*. The first row of the register detail table includes the register's description, the register's name, and the register's offset from the base peripheral address. The second row of the table is the header for the bit fields represented in the register. The third and subsequent rows of the table include the bit or bit range, the field name, the bit's or field's access, the reset value, and a description of the field. All registers are 32-bits unless specified otherwise. Reserved bits and fields are shown as **Reserved** in the description column. See *Table 1-1* for a list of all access types for each bit and field.

Table 1-3: Name 0 Register

| Name 0 |            |        |       | REG_NAME0                                         | [0x0000] |

|--------|------------|--------|-------|---------------------------------------------------|----------|

| Bits   | Field      | Access | Reset | Description                                       |          |

| 31:16  | -          | RO     | -     | Reserved                                          |          |

| 15:0   | field_name | R/W    | 0     | Field name description Description of field_name. |          |

Maxim Integrated Page 15 of 201

# 2. Overview

The MAX32660 is an ultra-low-power, cost-effective, highly integrated microcontroller designed for battery-powered devices and wireless sensors. It combines a flexible and versatile power management unit with the powerful Arm Cortex-M4 with FPU (Floating Point Unit). The device enables designs with complex sensor processing without compromising batt1ery life. It also offers legacy designs an easy and cost-optimal upgrade path from 8 or 16-bit microcontrollers. The device integrates up to 256KB of flash memory and 96KB of system RAM to accommodate application software.

The device features four powerful and flexible power modes. It can operate from a single supply battery voltage or a dual supply typically provided by a PMIC. The I<sup>2</sup>C (Inter-Integrated Circuit) port supports standard, fast, fast-plus, and high-speed modes operating up to 3400Kbps. The SPI ports can run up to 48MHz in both master and slave mode, and the UARTs can run up to 4Mbps. Three general-purpose 32-bit timers, a watchdog timer, and a real-time clock are also provided. An I<sup>2</sup>S (Inter-IC Sound) interface provides audio streaming to or from an external audio codec.

Figure 2-1: MAX32660 High-Level Block Diagram

Maxim Integrated Page 16 of 201

# 3. Memory, Register Mapping, and Access

# 3.1 Overview

The Arm Cortex-M4 core defines a standard memory space for unified code and data access. This memory space is addressed in units of single bytes but is most typically accessed in 32-bit (4 byte) units. It can also be accessed, depending on the implementation, in 8-bit (1 byte) or 16-bit (2 byte) widths. The total range of the memory space is 32-bits in width (4GB addressable total), from addresses 0x0000 0000 to 0xFFFF FFFF.

All flash, system RAM, the CPU, and peripheral registers are mapped between address 0x0000 0000 and 0x5FFF FFFF. See *Figure 3-1* and *Figure 3-2* for details on the mapping.

Maxim Integrated Page 17 of 201

Figure 3-1: Code Memory Mapping

Maxim Integrated Page 18 of 201

Figure 3-2: Data Memory Map

# 3.2 Standard Memory Regions

Several standard memory regions are defined for the Arm Cortex-M4 architecture; the use of many of these is optional for the system integrator. At a minimum, the MAX32660 must contain code and data memory for application code, stack and heap usage, and certain components of the implemented architecture.

Maxim Integrated Page 19 of 201

### 3.2.1 Code Space

The code space area of memory is designed to contain the primary memory used for code execution by the device. This memory area is defined from byte address range 0x0000 0000 to 0x1FFF FFFF (0.5GB maximum). The Cortex-M4 core and Arm debugger use two different standard core bus masters to access this memory area. The I-Code AHB bus master is used for instruction decode fetching from code memory, while the D-Code AHB bus master is used for data fetches from code memory. This is arranged so that data fetches avoid interfering with instruction execution.

On the MAX32660, the code space memory area contains the main internal flash memory that typically contains the instruction code executed on the device. The internal flash memory is mapped into both code and data space from 0x0000 0000 to 0x0003 FFFF. This program memory area must also contain the default system vector table and the initial settings for all system exception handlers and interrupt handlers. The reset vector for the device is 0x0000 0000. See *Interrupts and Exceptions* for details of the device interrupt vector table.

### 3.2.2 SRAM Space

The SRAM area of memory is intended to contain the device's primary SRAM data memory and is defined from byte address range 0x2000 0000 to 0x3FFF FFFF (0.5GB maximum). This memory can be used for general-purpose variable and data storage, code execution, and the Arm Cortex-M4 stack.

On the MAX32660, this memory area contains the main system SRAM, 96KB, that is mapped from 0x2000 0000 to 0x2001 7FFF.

The entirety of the SRAM memory space on the MAX32660 is contained within the dedicated Arm Cortex-M4's SRAM bit-banding region from 0x2000 0000 to 0x200F FFFF (1MB maximum for bit-banding). The CPU can access the entire SRAM either using standard byte/word/doubleword access or bit-banding operations. The bit-banding mechanism allows any single bit of any given SRAM byte address location to be set, cleared, or read individually by reading from or writing to a corresponding doubleword (32-bit wide) location in the bit-banding alias area.

The alias area for the SRAM bit-banding is located beginning at 0x2200 0000 and is a total of 32MB maximum, which allows the entire 1MB bit banding area to be accessed. Each 32-bit (4 byte aligned) address location in the bit-banding alias area translates into a single bit access (read or write) in the bit-banding primary area. Reading from the location performs a single bit read while writing either a 1 or 0 to the location performs a single bit set or clear.

Note: The Arm Cortex-M4 translates the access in the bit-banding alias area into the appropriate read cycle (for a single bit read) or a read-modify-write cycle (for a single bit set or clear) of the bit-banding primary area. Bit-banding is a core function (i.e., not a function of the SRAM memory interface layer or the AHB bus layer). This is only applicable to accesses generated by the core itself. Reads/writes to the bit-banding alias area by other (non-Arm -core) bus masters such as the Standard DMA AHB bus master does not trigger a bit-banding operation and instead results in an AHB bus error.

The SRAM area on the MAX32660 is capable of code execution. Code stored in the SRAM is accessed directly for execution using the system bus and is not cached. The SRAM is also where the Arm Cortex-M4 stack must be located, as it is the only general-purpose SRAM memory on the device. A valid stack location inside the SRAM must be set by the system exception table (which is, by default, stored at the beginning of the internal flash memory).

The MAX32660 specific AHB bus masters can also access the SRAM for general storage or working space.

### 3.2.3 Peripheral Space

The peripheral space area of memory is intended to map control registers, internal buffers/working space, and other features needed for the firmware control of non-core peripherals. It is defined from byte address range 0x4000 0000 to 0x5FFF FFFF (0.5GB maximum). On the MAX32660, all device-specific module registers are mapped to this memory area and any local memory buffers or FIFOs required by modules.

As with the SRAM region, there is a dedicated 1MB area at the bottom of this memory region (from 0x4000 0000 to 0x400F FFFF) used for bit-banding operations by the Arm Cortex-M4. Four-byte-aligned read/write operations in the

Maxim Integrated Page 20 of 201

peripheral bit-banding alias area (32MB in length, from 0x4200 0000 to 0x43FF FFFF) are translated by the core into read/mask/shift or read/modify/write operation sequences to the appropriate byte location in the bit-banding area.

Note: The bit-banding operation within peripheral memory space is, like bit-banding function in SRAM space, a core remapping function. As such, it is only applicable to operations performed directly by the Arm core. If another memory bus master (such as the Standard DMA AHB master) accesses the peripheral bit-banding alias region, the bit-banding remapping operation does not occur. In this case, the bit-banding alias region appears to be a non-implemented memory area (causing an AHB bus error).

On the MAX32660, access to the region that contains most peripheral registers (0x4000 0000 to 0x400F FFFF) goes from the AHB bus through an AHB-to-APB bridge. This allows the peripheral modules to operate on the slower, easier to handle APB bus matrix. This also ensures that peripherals with slower response times do not tie up bandwidth on the AHB bus, which must necessarily have a faster response time since it handles primary instruction and data fetching.

# 3.2.4 System Area (Private Peripheral Bus)

The system area (private peripheral bus) memory space contains register areas for functions that are only accessible by the Arm core itself (and the Arm debugger, in certain instances). It is defined from byte address range 0xE000 0000 to 0xE00F FFFF. This APB bus is restricted and can only be accessed by the Arm core and core-internal functions. It cannot be accessed by other modules which implement AHB memory masters, such as the DMA interface.

In addition to being restricted to the core, application code is only allowed to access this area when running in the privileged execution mode (instead of the standard user thread execution mode). This helps ensure that critical system settings controlled in this area are not altered inadvertently or by errant code that should not have access to this area.

Core functions controlled by registers mapped to this area include the SysTick timer, debug and tracing functions, the NVIC (interrupt handler) controller, and the Flash Breakpoint controller.

# 3.3 Device Memory Instances

This section details physical memory instances on the MAX32660 (including internal flash memory and SRAM instances) accessible as standalone memory regions using either the AHB or APB bus matrix. Memory areas that are only accessible through FIFO interfaces, or memory areas consisting of only a few registers for a peripheral, are not covered here.

#### 3.3.1 Main Program Flash Memory

The main program flash memory is 256KB in size and consists of 32 logical pages of 8,192 bytes per page.

### 3.3.2 Instruction Cache Memory

The internal flash memory instruction cache is 16KB in size and is used to cache instructions fetched using the I-Code bus. This includes instructions fetched from the internal flash memory.

Note: The cache is used for instruction fetches only. Data fetches (including code literal values) from the internal flash memory do not use the instruction cache.

### 3.3.3 Information Block Flash Memory

The information block is a separate flash instance used to store trim settings (option configuration and analog trim) and other nonvolatile device-specific information. The information block also contains the Unique Serial Number (USN). The USN has three parts labeled USNO, USN1, and USN2. USNO is 60 bits, while USN1 and USN2 are both 64 bits. Each USN can be read but cannot be written.

Maxim Integrated Page 21 of 201

Figure 3-3: Unique Serial Number Format

|                          |          |    | Bit Position     |                   |                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|--------------------------|----------|----|------------------|-------------------|------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|                          |          | 31 | 30               | 29                | 28               | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|                          | 0x40 000 | 0  | 0                | USN0 bits 29 - 0  |                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                          | 0x40 004 | 0  | 0                | USN0 bits 30 - 59 |                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Address                  | 0x40 008 |    | USN1 bits 31 - 0 |                   |                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Add                      | 0x4000C  |    |                  |                   | USN1 bits 32 -63 |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| 0x40010 USN2 bits 31 - 0 |          |    |                  |                   |                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                          | 0x40 014 |    | USN bits 32 - 63 |                   |                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

# 3.3.4 System SRAM

The system SRAM is 96KB in size and can be used for general-purpose data storage, the Arm Cortex-M4 system stack, and software code execution.

### 3.4 AHB Bus Matrix and AHB Bus Interfaces

This section details memory accessibility on the AHB bus matrix and the organization of AHB master and slave instances.

# 3.4.1 Core AHB Interface

#### 3.4.1.1 *I-Code*

The Arm core uses this AHB master for instruction fetching from memory instances located in code space from byte addresses 0x0000 0000 to 0x1FFF FFFF. This bus master is used to fetch instructions from the internal flash memory. Instructions fetched by this bus master are returned by the instruction cache, which in turn triggers a cache line fill cycle to fetch instructions from the internal flash memory when a cache miss occurs.

### 3.4.1.2 D-Code

The Arm Cortex-M4 core uses the D-Code AHB master for data fetches from memory instances located in code space from byte addresses 0x0000 0000 to 0x1FFF FFFF. The D-Code AHB master has access to the entire internal flash memory.

### 3.4.1.3 System

The Arm core uses AHB master for all instruction fetches and data read and write operations involving the SRAM. The APB mapped peripherals (through the AHB-to-APB bridge) and AHB mapped peripheral and memory areas are also accessed using this bus master.

### 3.4.2 AHB Slaves

### 3.4.2.1 Standard DMA

The standard DMA AHB slave has access to all off-core memory areas accessible by the system bus. It does not have access to the Arm Private Peripheral Bus area.

# 3.5 Peripheral Register Map

### 3.5.1 APB Peripheral Base Address Map

Table 3-1 contains the base address for each of the APB mapped peripherals. The base address for a given peripheral is the start of the register map for the peripheral. For a given peripheral, the register's address within the peripheral is defined as the peripheral base address plus the register's offset.

Maxim Integrated Page 22 of 201

Table 3-1: APB Peripheral Base Address Map

| Peripheral                     | Peripheral<br>Register<br>Prefix | Base Address | End Address |  |  |

|--------------------------------|----------------------------------|--------------|-------------|--|--|

| Global Control                 | GCR_                             | 0x4000 0000  | 0x4000 03FF |  |  |

| System Interface               | SIR_                             | 0x4000 0400  | 0x4000 07FF |  |  |

| Watchdog Timer 0               | WDT0_                            | 0x4000 3000  | 0x4000 33FF |  |  |

| Real-Time Clock                | RTC_                             | 0x4000 6000  | 0x4000 63FF |  |  |

| Power Sequencer                | PWRSEQ_                          | 0x4000 6800  | 0x4000 6BFF |  |  |

| GPIO Port 0                    | GPIO0_                           | 0x4000 8000  | 0x4000 8FFF |  |  |

| Timer 0                        | TMR0_                            | 0x4001 0000  | 0x4001 0FFF |  |  |

| Timer 1                        | TMR1_                            | 0x4001 1000  | 0x4001 1FFF |  |  |

| Timer 2                        | TMR2_                            | 0x4001 2000  | 0x4001 2FFF |  |  |

| SPIMSS (SPI1/I <sup>2</sup> S) | SPIMSS_                          | 0x4001 9000  | 0x4001 9FFF |  |  |

| I <sup>2</sup> C 0             | 12C0_                            | 0x4001 D000  | 0x4001 DFFF |  |  |

| I <sup>2</sup> C 1             | I2C1_                            | 0x4001 E000  | 0x4001 EFFF |  |  |

| Standard DMA                   | DMA_                             | 0x4002 8000  | 0x4002 8FFF |  |  |

| Flash Controller               | FLC_                             | 0x4002 9000  | 0x4002 93FF |  |  |

| Internal Cache Controller      | ICC_                             | 0x4002 A000  | 0x4002 AFFF |  |  |

| UART 0                         | UARTO_                           | 0x4004 2000  | 0x4004 2FFF |  |  |

| UART 1                         | UART1_                           | 0x4004 3000  | 0x4004 3FFF |  |  |

| SPI0                           | SPI17Y_                          | 0x4004 6000  | 0x4004 6FFF |  |  |

Maxim Integrated Page 23 of 201

# 4. System, Power, Clocks, Reset

The MAX32660 includes a high-frequency internal oscillator (HFIO), an 80kHz nano-ring oscillator (NANO), and support for an external 32kHz crystal or external clock. Support for selectable core operating voltage is provided, and the HFIO frequency is scaled based on the specific core operating voltage range selected.

# 4.1 Core Operating Voltage Range Selection

The MAX32660 supports three selections for the core operating voltage range (OVR). In a single-supply operation, changing the OVR sets the internal LDO regulator's output to the voltage shown in *Table 4-1*. In a dual-supply design, setting the OVR allows an external PMIC to dynamically provide the required V<sub>CORE</sub> voltage. Changing the OVR also reduces the output frequency of the HFIO, further reducing power consumption.

Changes to the OVR affect the internal flash memory access time, and the application software must set the flash wait states for each OVR setting as outlined in the section *Flash Wait States*. Changing the core operating voltage reduces the output frequency of the HFIO immediately, as shown in *Table 4-1*. Operating the device using dual external supplies requires special considerations and must be handled carefully in software.

Changing the core operating voltage reduces the output frequency of the HFIO immediately, as shown in *Table 4-1*. When operating the MAX32660 using dual external supplies requires special considerations and must be handled carefully in the application software.

|                | **     | _                         |                                  |                            | _                      |  |

|----------------|--------|---------------------------|----------------------------------|----------------------------|------------------------|--|

| PWRSEQ_LP_CTRL | FLC_CN | V <sub>CORE</sub> Typical | sys_osc                          |                            |                        |  |

| ovr            | lve    |                           | <i>f</i> <sub>нғю</sub><br>(МНz) | f <sub>NANO</sub><br>(kHz) | <i>f</i> хз2к<br>(kHz) |  |

| 0              | 1      | 0.9                       | 24                               | 80                         | 32.768                 |  |

| 1              | 1      | 1.0                       | 48                               | 80                         | 32.768                 |  |

|                |        |                           |                                  |                            |                        |  |

1.1

Table 4-1: OVR Selection and the Effect on V<sub>CORE</sub> and SYS OSC

# 4.1.1 Setting the Operating Voltage Range

The OVR selection is controlled using the power sequencer low-power control register field *PWRSEQ\_LP\_CTRL.ovr* which is only reset by a power-on reset (POR). This field should be checked after every reset to determine the correct clock speed and flash wait states. Adjusting the OVR setting affects the frequency of the HFIO. Before adjusting the OVR settings, it is required to set the system clock to either the 80kHz NANO or the 32.768kHz external RTC oscillator. The device coordinates OVR change between the internal LDO and the HFIO set frequency. When changing the OVR setting, the device must be operating from the internal LDO. In a system using an external supply for V<sub>CORE</sub>, software must transition to the internal LDO before changing the OVR setting.

96

80

32.768

The following steps describe how to change the OVR for devices that use the HFIO as the default SYS\_OSC:

- 1. Set PWRSEQ\_LP\_CTRL.Ido\_dis to 0 to ensure the device is operating from the internal LDO for Vcore.

- a. If using an external supply for V<sub>CORE</sub>, ensure the external supply is set to the same voltage as the current OVR setting. The external supply must be equal to or greater than the set OVR voltage.

- 2. Set either the 32.768kHz external RTC oscillator or the 80kHz NANO as the system clock source.

- a. See the Oscillator Sources and Clock Switching section for details on the system clock selection.

Maxim Integrated Page 24 of 201